这是西部数据在转向开放芯片规范之后,公布的第一款驱动器控制器核心。

在承诺将十亿个控制器核心转换为RISC-V设计之后,西部数据公司日前终于公布相关工作的最新结果。

西部数据方面曾于去年表示,其计划为自家专用驱动器控制器以及其它设备打造一套开放式的可扩展CPU架构。正如我们在当时的报道中所指出,那时大家还不太了解西部数据究竟在其磁盘与SSD控制器当中使用了怎样的控制器,只是普遍猜测其很可能为ARM兼容型芯片——例如ARM 9以及Cortex-M3等。唯一确定的是,西部数据公司在其ActiveScale归档系统以及Tegile全闪存与混合阵列当中使用的是英特尔CPU。

去年,这家磁盘与固态驱动器制造商强调称将把RISC-V作为未来的发展目标。作为承诺结果,西部数据一口气公布了SweRV核心、一套网络缓存一致性方案外加一款SweRV指令集模拟器。

西部数据公司CTO Martin Fink指出,数据需要更接近计算资源,但通用型CPU架构无法满足这一要求。RISC-V允许该公司利用开放标准接口实现以内存为中心的专用处理设计、特殊存储以及灵活的互连应用方式。

SweRV核心采用双工超标量设计,属于一种32位九级流水线核心,这意味着其能够同时加载多条指令并同时执行以节省处理时间。这亦是一种有序核心,其相对单核性能(模拟4.9 CoreMark/Mhz)有望超过大多数无序核心,例如ARM Coretex A15(实际为4.72 CoreMark/Mhz)。

其时钟速率最高可达1.8 GHz,且采用28纳米CMOS制程技术。

西部数据公司表示,其希望对这款核心进行开源,从而推动以数据为中心类应用的快速发展,具体包括物联网、安全处理以及工业控制等等。根据我们的理解,西部数据显然是希望将RISC-V CPU的使用范围推广到磁盘以及闪存驱动器控制器以外。

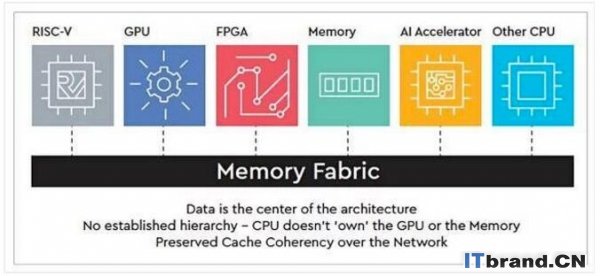

OmniXtend是一套开放式品牌方案,可通过以太网结构提供缓存一致性内存。缓存一致性机制确保多个共享缓存内存的处理器之间始终保持同步。

OmniXtend负责为各处理器、机器学习加速器、GPU、FPGA以及其它组件之间的访问与数据共享操作提供开放标准接口。

在这里我们需要强调一点:磁盘与SSD控制器通常并不需要缓存一致性方案,因此西部数据的技术野心显然是要在系统级别的堆栈当中占据一席之地。

西部数据指出,OmniXtend可以为未来的连接计算、存储、内存以及I/O组件的运行结构提供潜在支持。

这听起来更像是在描述系统可组合性,而西部数据方面已经凭借着此前的OpenFlex硬件与软件成功进入可组合系统领域当中。

为了帮助提升RISC-V生态系统与SweRV设计的未来发展空间,西部数据公司还开放了一款SweRV指令集模拟器(简称ISS)。这意味着用户可以借此对外部事件——例如中断与总线错误——进行建模,从而确保RISC-V核心的正常运行。

由于西部数据将其绝大部分核心部署至磁盘以及闪存驱动器的控制器当中,因此面向RISC-V设计的迁移工作对于此类嵌入式系统之外的世界而言基本上不会带来直观感受。

如果该公司开发出64位RISC-V技术并在系统层级内加以使用——例如用以取代x86处理器,那么RISC-V将真正暴露在公众视野当中。此外,这一举措也将帮助西部数据降低产品成本,意味着其不再需要为此类系统购买英特尔CPU或者ARM授权许可。